# LIN Bus Device Family Including Voltage Regulator and LIN SBC with Compatible Footprint

#### **Features**

- · ISO 26262 Functional Safety Ready

- · Supply Voltage up to 40V

- Operating Voltage V<sub>VS</sub> = 5V to 28V

- · Supply Current

- Sleep mode: typically 9 μA

- Silent mode: typically 47 μA

- Very low current consumption at low supply voltages (2V <  $V_{VS}$  < 5.5V): typically 130  $\mu A$

- Linear Low-Drop Voltage Regulator, 85 mA Current Capability:

- MLC (multi-layer ceramic) capacitor with  $0\Omega$   $\mbox{FSR}$

- Normal, Fail-Safe and Silent mode

- ATA663254: V<sub>VCC</sub> = 5.0V, ±2%

- ATA663231:  $V_{VCC}$  = 3.3V, ±2%

- · Sleep Mode: VCC is Switched Off

- · Active Mode:

- ATA663203: V<sub>VCC</sub> = 5.0V, ±2%

- ATA663201:  $V_{VCC}$  = 3.3V, ±2%

- VCC Undervoltage Detection with Open Drain Reset Output (NRES, 4 ms Reset Time)

- Voltage Regulator is Short-Circuit and Overtemperature Protected

- LIN Physical Layer According to LIN 2.0, 2.1, 2.2, 2.2A, ISO 17987-4 and SAEJ2602-2

- Wake-Up Capability via LIN Bus (100 μs Dominant)

- · Wake-Up Source Recognition

- TXD Time-Out Timer

- Bus Pin is Overtemperature and Short-Circuit Protected Versus GND and Battery

- · Advanced EMC and ESD Performance

- Fulfills the OEM "Hardware Requirements for LIN in Automotive Applications Rev.1.3"

- Interference and Damage Protection According to ISO7637

- AEC-Q100 and AEC-Q006 Qualified

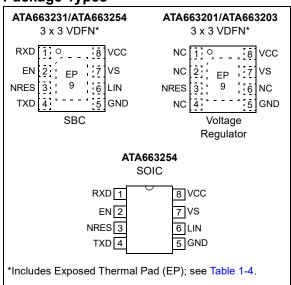

- Packages:

- 8-Lead 3 x 3 VDFN (all types) with wettable flanks (Moisture Sensitivity Level 1)

- 8-Lead SOIC (only ATA663254)

Note: LIN SBC: LIN system basis chip including LIN transceiver and voltage regulator.

#### **Description**

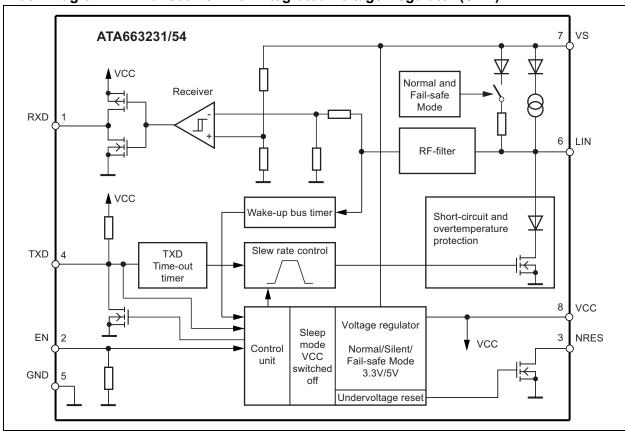

The ATA663201/03/31/54 device family includes two basic products: a LIN system basis chip (SBC) and a low-drop voltage regulator with compatible footprints.

The ATA663231/54 (SBC) is a fully-integrated LIN transceiver, designed according to the LIN specification 2.0, 2.1, 2.2, 2.2A, ISO 17987-4 and SAEJ2602-2, with a low-drop voltage regulator (3.3V/5V/85 mA). The combination of voltage regulator and bus transceiver makes it possible to develop simple but powerful slave nodes in LIN bus systems.

The ATA663231/54 is designed to handle the low-speed data communication in vehicles (for example, in convenience electronics). Improved slope control at the LIN driver ensures secure data communication up to 20 Kbaud. The bus output is designed to withstand high voltage. Sleep mode and Silent mode ensure minimized current consumption even in the case of a floating or a short-circuited LIN bus.

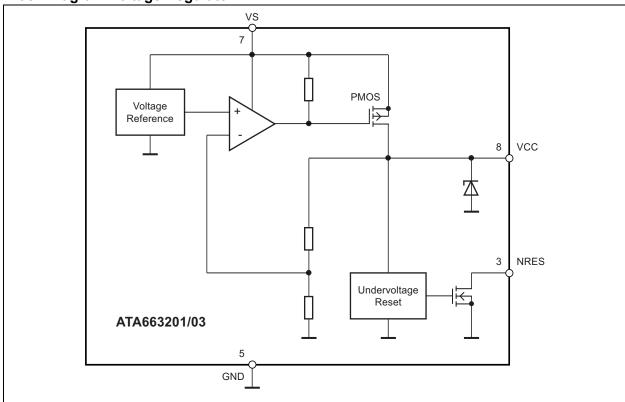

The ATA663201/03 (voltage regulator) is a fully integrated low-drop voltage regulator, with 3.3V/5V output voltage and 85 mA current capability. It is especially designed for the automotive environment. A key feature is that the current consumption is always below 170  $\mu$ A (without load), even if the supply voltage is below the regulator's nominal output voltage.

#### Package Types

TABLE 1: ATA663201/03/31/54 FAMILY MEMBERS

| Device    | Description                 |

|-----------|-----------------------------|

| ATA663231 | LIN-SBC with 3.3V regulator |

| ATA663254 | LIN-SBC with 5V regulator   |

| ATA663201 | Voltage regulator 3.3V      |

| ATA663203 | Voltage regulator 5V        |

## **Block Diagram LIN Transceiver with Integrated Voltage Regulator (SBC)**

## **Block Diagram Voltage Regulator**

#### 1.0 **FUNCTIONAL DESCRIPTION**

#### 1.1 **Physical Layer Compatibility**

Since the LIN physical layer is independent of higher LIN layers (e.g., LIN protocol layer), all nodes with a LIN physical layer according to revision 2.x can be mixed with LIN physical layer nodes based on earlier versions (i.e., LIN 1.0, LIN 1.1, LIN 1.2, LIN 1.3) without any restrictions.

#### 1.2 **Operating Modes**

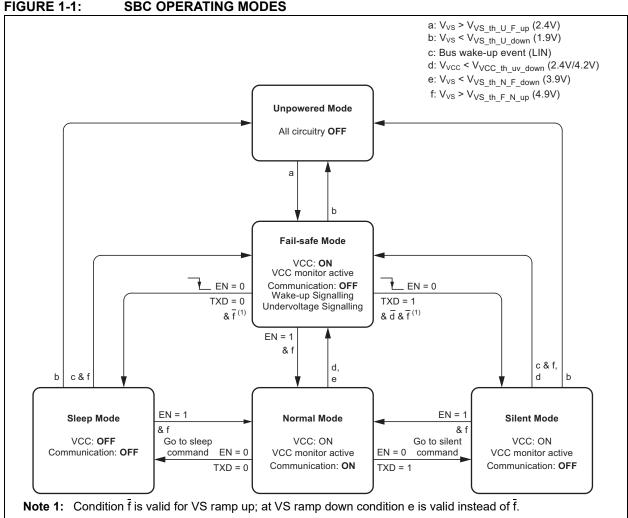

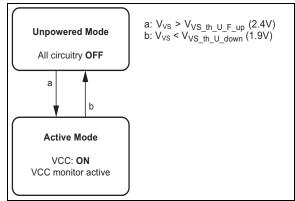

FIGURE 1-1: **SBC OPERATING MODES**

**TABLE 1-1:** SBC (ATA663254, ATA663231) OPERATING MODES

| Operating Mode  | Transceiver | V <sub>VCC</sub> (SBC Only) | LIN           | TXD                                         | RXD  |  |

|-----------------|-------------|-----------------------------|---------------|---------------------------------------------|------|--|

| Fail-Safe       | OFF         | 3.3V/5V                     | Recessive     | Signaling fail-safe sources (see Table 1-2) |      |  |

| Normal          | OFF         | 3.3V/5V                     | TXD-dependent | Follows data transmission                   |      |  |

| Silent          | OFF         | 3.3V/5V                     | Recessive     | High                                        | High |  |

| Sleep/Unpowered | OFF         | 0V                          | Recessive     | Low                                         | Low  |  |

FIGURE 1-2: VOLTAGE REGULATOR OPERATING MODES

#### 1.2.1 NORMAL MODE (SBC ONLY)

This is the Normal transmitting and receiving mode of the LIN Interface, in accordance with LIN specification 2.x.

The VCC voltage regulator operates with a 3.3V/5V output voltage, with a low tolerance of ±2% and a maximum output current of 85 mA. If an undervoltage condition occurs, NRES switches to low and the IC changes its state to Fail-Safe mode.

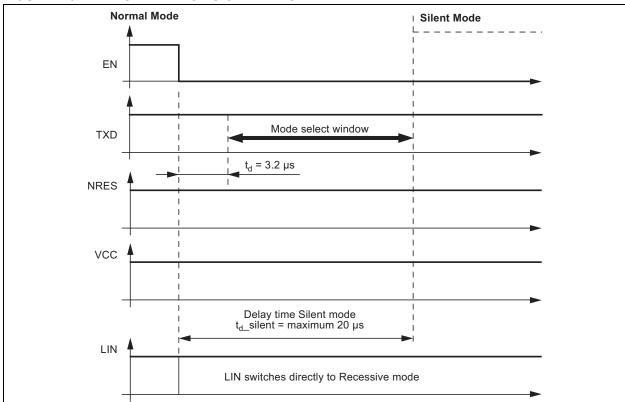

#### 1.2.2 SILENT MODE (SBC ONLY)

A falling edge at EN while TXD is high switches the IC into Silent mode. The TXD signal has to be logic high during the mode select window. The transmission path is disabled in Silent mode. The voltage regulator is active. The overall supply current from  $V_{Bat}$  is a combination of the  $I_{VSsilent}$  = 47  $\mu A$  plus the VCC regulator output current  $I_{VCC}$ .

FIGURE 1-3: SWITCHING TO SILENT MODE

In Silent mode, the internal slave termination between the LIN pin and VS pin is disabled to minimize the current consumption in case the pin LIN is short-circuited to GND. Only a weak pull-up current (typically 10  $\mu\text{A})$  between the LIN pin and VS pin is present. Silent mode can be activated independently from the current level on pin LIN.

If an undervoltage condition occurs, NRES is switched to low and the Microchip SBC changes its state to Fail-Safe mode.

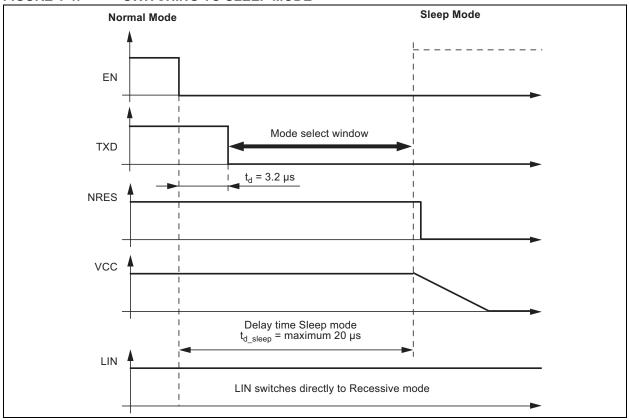

#### 1.2.3 SLEEP MODE (SBC ONLY)

A falling edge at EN while TXD is low switches the IC into Sleep mode. The TXD signal has to be logic low during the mode select window (Figure 1-6).

FIGURE 1-4: SWITCHING TO SLEEP MODE

In order to avoid any influence to the LIN pin when switching into Sleep mode, it is possible to switch EN up to  $3.2~\mu s$  earlier to low than TXD. The easiest and best way to do this is by having two falling edges at TXD and EN at the same time.

In Sleep mode, the transmission path is disabled. Supply current from  $V_{Bat}$  is typically  $I_{VSsleep}$  = 9  $\mu A.$  The VCC regulator is switched off; NRES and RXD are low. The internal slave termination between the LIN pin and VS pin is disabled to minimize the current consumption in case the LIN pin is short-circuited to GND.

Only a weak pull-up current (typically 10  $\mu$ A) between the LIN pin and the VS pin is present. The Sleep mode can be activated independently from the current level on the LIN pin.

Voltage below the LIN pre-wake detection  $V_{\text{LINL}}$  at the LIN pin activates the internal LIN receiver and starts the wake-up detection timer.

If the TXD pin is short-circuited to GND, it is possible to switch to Sleep mode via EN after  $t > t_{dom}$ .

#### 1.2.4 FAIL-SAFE MODE (SBC ONLY)

The device automatically switches to Fail-Safe mode at system power-up. The voltage regulator is switched on. The NRES output remains low for  $t_{\rm res} = 4~{\rm ms}$  and causes the microcontroller to be reset. LIN communication is switched off. The IC stays in this mode until EN is switched to high. The IC then changes to Normal mode. A low at NRES switches the IC into Fail-Safe mode directly. During Fail-Safe mode, the TXD pin is an output and, together with the RXD output pin, signals the Fail-Safe source.

If the device enters the Fail-Safe mode coming from the Normal mode (EN = 1) due to a VS undervoltage condition ( $V_{VS} < V_{VS\_th\_N\_F\_down}$ ), it is possible to switch into sleep or silent mode by a falling edge at the EN input. With this feature the current consumption can be further reduced.

A wake-up event from either Silent or Sleep mode is signaled to the microcontroller using the RXD pin and the TXD pin. A VS undervoltage condition is also signaled at these two pins. The coding is shown in Table 1-2.

A wake-up event switches the IC to Fail-Safe mode.

TABLE 1-2: SIGNALING IN FAIL-SAFE MODE

| Fail-Safe Sources                                                          | TXD  | RXD |

|----------------------------------------------------------------------------|------|-----|

| LIN wake-up (LIN pin)                                                      | Low  | Low |

| VS <sub>th</sub> (battery) undervoltage detection (V <sub>VS</sub> < 3.9V) | High | Low |

## 1.3 Wake-Up Scenarios from Silent Mode or Sleep Mode

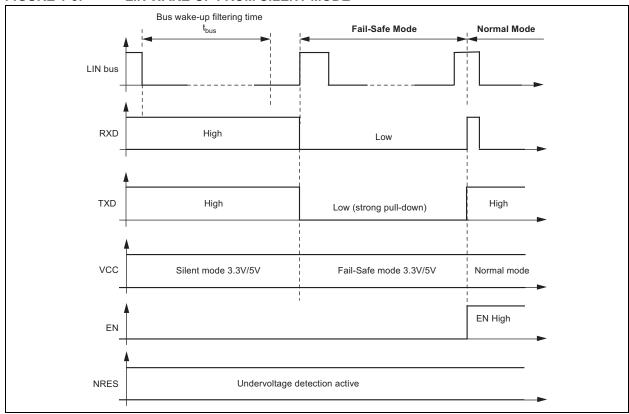

#### 1.3.1 REMOTE WAKE-UP VIA LIN BUS

## 1.3.1.1 Remote Wake-Up from Silent Mode (SBC only)

A remote wake-up from Silent mode is only possible if TXD is high. A voltage less than the LIN pre-wake detection VLINL at the LIN pin activates the internal LIN receiver and starts the wake-up detection timer. A

falling edge at the LIN pin followed by a dominant bus level maintained for a certain period of time (>t<sub>bus</sub>) and the following rising edge at pin LIN (see Figure 1-5) result in a remote wake-up request. The device switches from Silent mode to Fail-Safe mode, the VCC voltage regulator remains activated and the internal LIN slave termination resistor is switched on. The remote wake-up request is indicated by a low level at the RXD pin and TXD pin (strong pull-down at TXD). EN high can be used to switch directly to Normal mode.

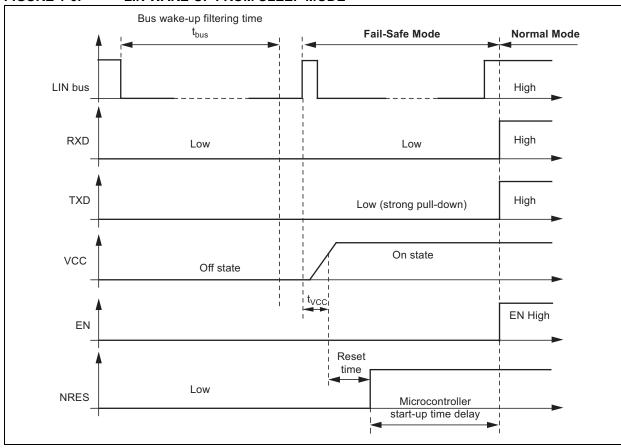

FIGURE 1-5: LIN WAKE-UP FROM SILENT MODE

## 1.3.1.2 Remote Wake-Up from Sleep Mode (SBC only)

A falling edge at the LIN pin followed by a dominant bus level maintained for a certain period of time ( $>t_{bus}$ ) and a following rising edge at the LIN pin result in a remote wake-up request, causing the device to switch from Sleep mode to Fail-Safe mode.

The VCC regulator is activated, and the internal LIN slave termination resistor is switched on. The remote wake-up request is indicated by a low level at RXD and TXD (strong pull-down at TXD) (see Figure 1-6).

EN high can be used to switch directly from Sleep/ Silent mode to Fail-Safe mode. If EN is still high after VCC ramp-up and undervoltage reset time, the IC switches to Normal mode.

FIGURE 1-6: LIN WAKE-UP FROM SLEEP MODE

## 1.3.2 WAKE-UP SOURCE RECOGNITION (SBC ONLY)

The device can distinguish between different wake-up sources. The wake-up source can be read on the TXD and RXD pin in Fail-Safe mode. These flags are immediately reset if the microcontroller sets the EN pin to high and the IC is in Normal mode.

TABLE 1-3: SIGNALING IN FAIL-SAFE MODE

| Fail-Safe Sources                                                          | TXD  | RXD |

|----------------------------------------------------------------------------|------|-----|

| LIN wake-up (LIN pin)                                                      | Low  | Low |

| VS <sub>th</sub> (battery) undervoltage detection (V <sub>VS</sub> < 3.9V) | High | Low |

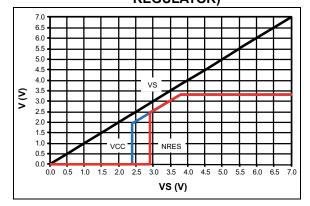

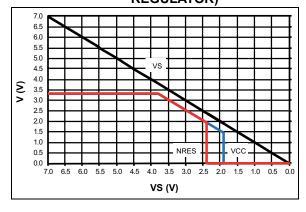

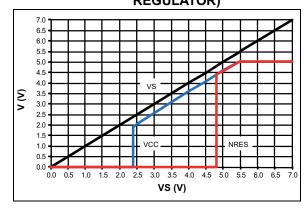

# 1.4 Behavior Under Low Supply Voltage Condition

After the battery voltage has been connected to the application circuit, the voltage at the VS pin increases according to the block capacitor used in the application (see Figure 1-14). If  $V_{VS}$  is higher than the minimum VS operation threshold  $V_{VS\_th\_U\_F\_up},$  the IC mode changes from unpowered mode to Fail-Safe mode. As soon as  $V_{VS}$  exceeds the undervoltage threshold  $V_{VS\_th\_F\_N\_up},$  the LIN transceiver can be activated.

The VCC output voltage reaches its nominal value after  $t_{VCC}$ . This parameter depends on the externally applied VCC capacitor and the load. The NRES output is low for the reset time delay  $t_{reset}$ . No mode change is possible during this time  $t_{reset}$ .

The behavior of VCC, NRES and VS is shown in Figures 1-7 to Figure 1-10 (ramp-up and ramp-down).

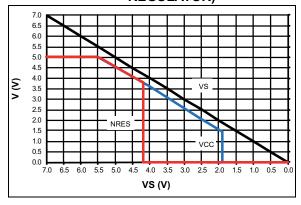

FIGURE 1-7: VCC AND NRES VERSUS

VS (RAMP-UP) FOR 3.3V

(SBC AND VOLTAGE

REGULATOR)

FIGURE 1-8: VCC AND NRES VERSUS

VS (RAMP-DOWN) FOR

3.3V (SBC AND VOLTAGE

REGULATOR)

FIGURE 1-9: VCC AND NRES VERSUS

VS (RAMP-UP) FOR 5V

(SBC AND VOLTAGE

REGULATOR)

FIGURE 1-10: VCC AND NRES VERSUS

VS (RAMP-DOWN) FOR 5V

(SBC AND VOLTAGE

REGULATOR)

The upper graphs are only valid if the VS ramp-up and ramp-down times are much slower than the VCC ramp-up time  $t_{VCC}$  and the NRES delay time  $t_{reset}$ .

If during Sleep mode the voltage level of  $V_{VS}$  drops below the undervoltage detection threshold  $V_{VS\_th\_N\_F\_down}$  (typical 4.3V), the operation mode is not changed and no wake-up is possible. The IC switches to unpowered mode only if the supply voltage on pin VS drops below the VS operation threshold  $V_{VS\_th\_U\_down}$  (typical 2.05V).

If during Silent mode the VCC voltage drops below the VCC undervoltage threshold  $V_{VCC\_th\_uv\_down},$  the IC switches into Fail-Safe mode. If the supply voltage on pin VS drops below the VS operation threshold  $V_{VS\_th\_U\_down}$  (typical 2.05V), the IC switches to unpowered mode.

If during Normal mode the voltage level on the VS pin drops below the VS undervoltage detection threshold  $V_{VS\_th\_N\_F\_down}$  (typical 4.3V), the IC switches to Fail-Safe mode. This means the LIN transceiver is disabled in order to avoid malfunctions or false bus messages. The voltage regulator remains active.

- For 3.3V SBC: In this undervoltage situation it is possible to switch the device into Sleep mode or Silent mode by a falling edge at the EN input. For this feature, switching into these two current saving modes is always guaranteed, allowing current consumption to be reduced even further. When the VCC voltage drops below the VCC undervoltage threshold V<sub>VCC\_th\_uv\_down</sub> (typical 2.6V) the IC switches into Fail-Safe mode.

- For 5V SBC: Because of the VCC undervoltage condition in this situation, the IC is in Fail-Safe mode and can be switched into Sleep mode only. The IC switches into unpowered mode only when the supply voltage Vvs drops below the operation threshold V<sub>VS th U down</sub> (typical 2.05V).

The current consumption of the SBC in Silent mode or in Fail-Safe mode and the one of the voltage regulator is always below 170  $\mu A,$  even when the supply voltage  $V_{VS}$  is lower than the regulator's nominal output voltage  $V_{VCC}.$

### 1.5 Voltage Regulator

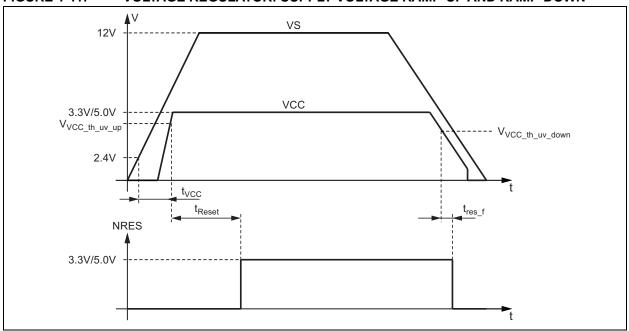

FIGURE 1-11: VOLTAGE REGULATOR: SUPPLY VOLTAGE RAMP-UP AND RAMP-DOWN

The voltage regulator needs an external capacitor for compensation and to smooth the disturbances from the microcontroller. It is recommended to use a MLC capacitor with a minimum capacitance of 1.8  $\mu\text{F}$  together with a 100 nF ceramic capacitor. Depending on the application, the values of these capacitors can be modified by the customer.

During a short circuit at VCC, the output limits the output current to  $I_{VCClim}.$  Because of undervoltage, NRES switches to low and sends a reset to the microcontroller. If the chip temperature exceeds the value  $T_{VCCoff},$  the VCC output switches off. The chip cools down and, after a hysteresis of  $T_{hys},$  switches the output on again.

When the ATA663201/03/31/54 in the 8-Lead VDFN package is being soldered onto the Printed Circuit Board (PCB) it is mandatory to connect the heat slug with a wide GND plate on the printed board to get a good heat sink.

The main power dissipation of the IC is created from the VCC output current  $I_{VCC}$ , which is needed for the application.

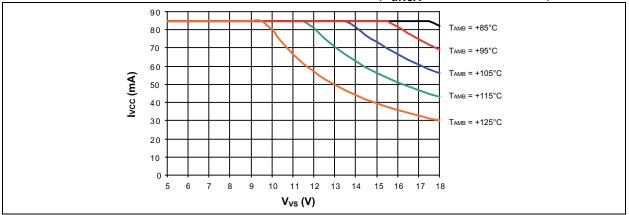

Figure 1-12 shows the safe operating area of the ATA663201/03/31/54 in the 8-Lead VDFN package.

FIGURE 1-12: 8-LEAD VDFN PACKAGE POWER DISSIPATION: SAFE OPERATING AREA: REGULATOR'S OUTPUT CURRENT  $I_{VCC}$  VERSUS SUPPLY VOLTAGE  $V_{VS}$  AT DIFFERENT AMBIENT TEMPERATURES ( $R_{thv,IA}$  = 50K/W ASSUMED)

When the ATA663254 in its special 8-Lead SOIC package (fused lead frame to pin 5) is being soldered on to the PCB, it is mandatory to connect pin 5 with a wide GND plate on the printed board to get a good heat sink.

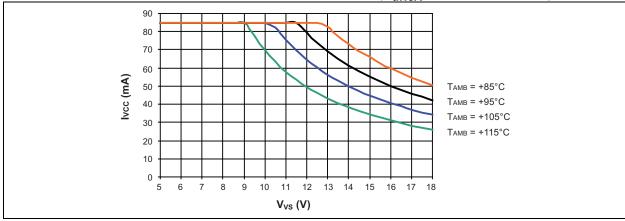

Figure 1-13 shows the safe operating area of the ATA663254 in the 8-Lead SOIC package.

FIGURE 1-13: 8-LEAD SOIC PACKAGE POWER DISSIPATION: SAFE OPERATING AREA: REGULATOR'S OUTPUT CURRENT  $I_{VCC}$  VERSUS SUPPLY VOLTAGE  $V_{VS}$  AT DIFFERENT AMBIENT TEMPERATURES ( $R_{thvJA}$  = 80K/W ASSUMED)

#### 1.6 Pin Descriptions

The descriptions of the pins are listed in Table 1-4.

TABLE 1-4: PIN FUNCTION TABLE

| ATA663201  | ATA663203  | ATA663231  | ATA663254           |        |                                                                   |

|------------|------------|------------|---------------------|--------|-------------------------------------------------------------------|

| 3 x 3 VDFN | 3 x 3 VDFN | 3 x 3 VDFN | 3 x 3 VDFN/<br>SOIC | Symbol | Description                                                       |

|            | _          | 1          | 1                   | RXD    | Receive Data Output                                               |

| _          | _          | 2          | 2                   | EN     | Enables Normal Mode if the Input is High                          |

| 3          | 3          | 3          | 3                   | NRES   | VCC Undervoltage Output, Open Drain, Low at Reset                 |

| _          | _          | 4          | 4                   | TXD    | Transmit Data Input                                               |

| 5          | 5          | 5          | 5                   | GND    | Ground                                                            |

| 6          | 6          | 6          | 6                   | LIN    | LIN Bus Line Input/Output                                         |

| _          | _          | 7          | 7                   | VS     | Supply Voltage                                                    |

| 8          | 8          | 8          | 8                   | VCC    | Output Voltage Regulator 3.3V/5V/85 mA                            |

| 1,2,4,6    | 1,2,4,6    | _          |                     | NC     | Not Connected                                                     |

| EP         | EP         | EP         | EP                  | EP     | Exposed Thermal Pad, Internally Connected to the GND pin (Note 1) |

Note 1: Only for the VDFN package.

#### 1.6.1 OUTPUT PIN (RXD) (SBC ONLY)

In Normal mode this pin reports the state of the LIN bus to the microcontroller. LIN high (recessive state) is indicated by a high level at RXD; LIN low (dominant state) is indicated by a low level at RXD.

The output is a push-pull stage switching between VCC and GND. The AC characteristics are measured by an external load capacitor of 20 pF.

In Silent mode, the RXD output switches to high.

## 1.6.2 ENABLE INPUT PIN (EN) (SBC ONLY)

The enable input pin controls the operating mode of the device. If EN is high, the circuit is in Normal mode, with transmission paths from TXD to LIN and from LIN to RXD both active. The VCC voltage regulator operates with 3.3V/5V/85 mA output capability.

If EN is switched to low while TXD is still high, the device is forced to Silent mode. No data transmission is then possible, and current consumption is reduced to  $I_{VSsilent}$  typical 47  $\mu A.$  The VCC regulator retains its full functionality.

If EN is switched to low while TXD is low, the device is forced to Sleep mode. No data transmission is possible and the voltage regulator is switched off.

The EN pin provides a pull-down resistor to force the transceiver into Recessive mode if EN is disconnected.

## 1.6.3 UNDERVOLTAGE RESET OUTPUT (NRES)

If the VCC voltage falls below the undervoltage detection threshold  $V_{VCC\_th\_uv\_down}, \ NRES$  switches to low after  $t_{res\_f}.$  The NRES stays low even if  $V_{VCC}$  = 0V because NRES is internally driven from the VS voltage. If the VS voltage ramps down, NRES stays low until  $V_{VS}$  < 1.5V and then becomes highly impedant.

The implemented undervoltage delay keeps NRES low for  $t_{Reset}$  = 4 ms after  $V_{VCC}$  reaches its nominal value.

#### 1.6.4 INPUT/OUTPUT (TXD) (SBC ONLY)

In Normal mode, the TXD pin is the microcontroller interface for controlling the state of the LIN output. TXD must be pulled to ground in order to drive the LIN bus low. If TXD is high or unconnected (internal pull-up resistor), the LIN output transistor is turned off and the bus is in the recessive state. If the TXD pin stays at GND level while switching into Normal mode, it must be pulled to high level longer than 10 µs before the LIN driver can be activated. This feature prevents the bus line from being accidentally driven to dominant state after the Normal mode has been activated (also in case of a short circuit at TXD to GND). During Fail-Safe mode, this pin is used as output and signals the fail-safe source.

The TXD input has an internal pull-up resistor.

An internal timer prevents the bus line from being driven permanently in the dominant state. If TXD is forced to low longer than  $t_{\rm dom}$  > 20 ms, the LIN bus driver is switched to the recessive state. Nevertheless, when switching to Sleep mode, the actual level at the TXD pin is relevant.

To reactivate the LIN bus driver, switch TXD to high (> 10  $\mu$ s).

#### 1.6.5 GROUND PIN (GND)

The IC does not affect the LIN bus in the event of GND disconnection. It is able to handle a ground shift of up to 11.5% of  $V_{\rm VS}$ .

#### 1.6.6 BUS PIN (LIN) (SBC ONLY)

A low-side driver with internal current limitation and thermal shutdown as well as an internal pull-up resistor according to LIN specification 2.x is implemented. The voltage range is from -27V to +40V. This pin exhibits no reverse current from the LIN bus to VS, even in the event of a GND shift or  $V_{Bat}$  disconnection. The LIN receiver thresholds comply with the LIN protocol specification.

The fall time (from recessive to dominant) and the rise time (from dominant to recessive) are slope-controlled.

During a short circuit at LIN to  $V_{Bat}$ , the output limits the output current to  $I_{BUS\_LIM}$ . Due to the power dissipation, the chip temperature exceeds  $T_{LINoff}$  and the LIN output is switched off. The chip cools down and after a hysteresis of  $T_{hys}$ , switches the output on again. RXD stays on high because LIN is high. The VCC regulator works independently during LIN overtemperature switch-off.

During a short circuit from LIN to GND, the IC can be switched into Sleep or Silent mode and even in this case the current consumption is lower than 100  $\mu$ A in Sleep mode and lower than 120  $\mu$ A in Silent mode. If the short-circuit disappears, the IC starts with a remote wake-up.

The reverse current is  $<2 \,\mu\text{A}$  at pin LIN during loss of  $V_{Bat}$ . This is optimal behavior for bus systems where some slave nodes are supplied from battery or ignition.

#### 1.6.7 SUPPLY PIN (VS)

LIN operating voltage is  $V_{VS}$  = 5V to 28V. Undervoltage detection is implemented to disable transmission if  $V_{VS}$  falls below typical 4.5V, thereby avoiding false bus messages. After switching on  $V_{VS}$ , the IC starts in Fail-Safe mode and the voltage regulator is switched on.

The supply current in Sleep mode is typically 9  $\mu$ A and 47  $\mu$ A in Silent mode.

## 1.6.8 VOLTAGE REGULATOR OUTPUT PIN (VCC)

The internal 3.3V/5V voltage regulator is capable of driving loads up to 85 mA, supplying the microcontroller and other ICs on the PCB and is protected against overload by means of current limitation and overtemperature shutdown. Furthermore, the output voltage is monitored and causes a reset signal at the NRES output pin if it drops below a defined threshold  $V_{\rm VCC\ th\ uv\ down}$

### 1.7 Typical Applications

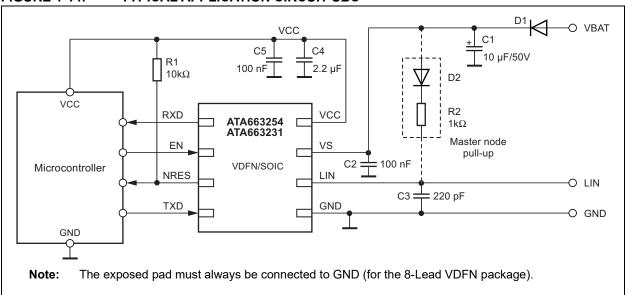

#### FIGURE 1-14: TYPICAL APPLICATION CIRCUIT SBC

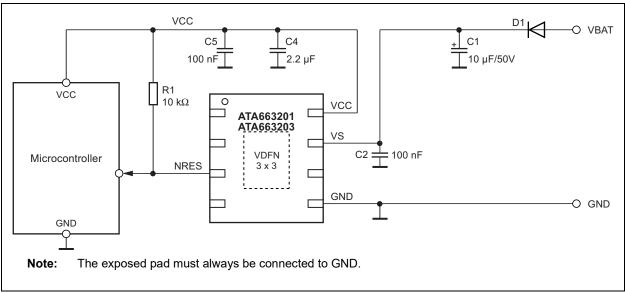

### FIGURE 1-15: TYPICAL APPLICATION CIRCUIT VOLTAGE REGULATOR

### 2.0 ELECTRICAL CHARACTERISTICS

### 2.1 Absolute Maximum Ratings†

| Supply Voltage (V <sub>VS</sub> )                                                           | 0.3V to +40V   |

|---------------------------------------------------------------------------------------------|----------------|

| $V_{VS}$ , Pulse Time $\leq$ 500 ms, $T_{amb}$ = +25°C, Output Current $I_{VCC} \leq$ 85 mA | +40V           |

| $V_{VS}$ , Pulse Time $\leq$ 2 min, $T_{amb}$ = +25°C, Output Current $I_{VCC} \leq$ 85 mA  | +28V           |

| Logic Pins:                                                                                 |                |

| Voltage Level (RXD, TXD, EN, NRES) (V <sub>Logic</sub> )                                    | 0.3 to +5.5V   |

| Output DC Currents (I <sub>Logic</sub> )                                                    | 5 mA to +5 mA  |

| LIN:                                                                                        |                |

| DC Voltage (V <sub>LIN</sub> )                                                              | 27V to +40V    |

| Pulse Time < 500 ms (V <sub>LIN</sub> )                                                     | +43.5V         |

| VCC:                                                                                        |                |

| DC Voltage (V <sub>VCC</sub> )                                                              | -0.3V to +5.5V |

| DC Input Current (I <sub>VCC</sub> )                                                        | +200 mA        |

| ESD according to IBEE LIN EMC; test specification 1.0 following IEC 61000-4-2               |                |

| Pin VS, LIN to GND (with external circuitry, according to applications diagram)             | ±6 kV          |

| ESD HBM following STM5.1 with 1.5 k $\Omega$ /100 pF                                        |                |

| Pin VS, LIN to GND                                                                          |                |

| HBM ESD ANSI/ESD-STM5.1 JESD22-A114 AEC-Q100 (002)                                          | ±3 kV          |

| CDM ESD STM 5.3.1                                                                           | ±750V          |

| Machine Model ESD AEC-Q100-RevF(003)                                                        | ±200V          |

| Virtual Junction Temperature (T <sub>vJ</sub> )                                             |                |

| Storage Temperature (T <sub>stg</sub> )                                                     | 55°C to +150°C |

|                                                                                             |                |

**<sup>†</sup> NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device, at those or any other conditions above those indicated in the operational listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

**Electrical Characteristics**: Unless otherwise indicated, all values are specified for  $5V < V_{VS} < 28V$ ,  $-40^{\circ}C < T_{vJ} < +150^{\circ}C$  and refer to the GND pin.

| No. | Parameters                                                         | Symbol                      | Min. | Тур. | Max. | Unit | Conditions                                                                                                |

|-----|--------------------------------------------------------------------|-----------------------------|------|------|------|------|-----------------------------------------------------------------------------------------------------------|

| 1   | VS Pin                                                             | -                           |      |      | l    |      |                                                                                                           |

| 1.1 | Nominal DC<br>Voltage Range                                        | VS                          | 5    | 13.5 | 28   | V    |                                                                                                           |

| 1.2 | Supply Current in<br>Sleep Mode                                    | I <sub>VSsleep</sub>        | 6    | 9    | 12   | μA   | Sleep mode $V_{LIN} > V_{VS} - 0.5V$ $V_{VS} < 14V$ , T = +27°C (Note 1)                                  |

|     |                                                                    | I <sub>VSsleep</sub>        | 3    | 10   | 15   | μA   | Sleep mode $V_{LIN} > V_{VS} - 0.5V$ $V_{VS} < 14V$                                                       |

|     |                                                                    | I <sub>VSsleep_short</sub>  | 20   | 50   | 100  | μA   | Sleep mode,<br>V <sub>LIN</sub> = 0V<br>bus shorted to GND<br>V <sub>VS</sub> < 14V                       |

| 1.3 | Supply Current in<br>Silent Mode (SBC)<br>/Active Mode<br>(Voltage | I <sub>VSsilent</sub>       | 30   | 47   | 58   | μA   | Bus recessive $5.5V < V_{VS} < 14V$ without load at VCC $T = +27^{\circ}C$ (Note 1)                       |

|     | Regulator)                                                         | I <sub>VSsilent</sub>       | 30   | 50   | 64   | μA   | Bus recessive<br>5.5V <v<sub>VS &lt; 14V<br/>without load at VCC</v<sub>                                  |

|     |                                                                    | I <sub>VSsilent</sub>       | 50   | 130  | 170  | μA   | Bus recessive<br>2.0V < V <sub>VS</sub> < 5.5V<br>without load at VCC                                     |

|     |                                                                    | I <sub>VSsilent_short</sub> | 50   | 80   | 120  | μA   | Silent mode<br>5.5V < V <sub>VS</sub> < 14V<br>bus shorted to GND<br>without load at VCC                  |

| 1.4 | Supply Current in<br>Normal Mode                                   | l <sub>VSrec</sub>          | 150  | 230  | 300  | μA   | Bus recessive<br>V <sub>VS</sub> < 14V<br>without load at VCC                                             |

| 1.5 | Supply Current in<br>Normal Mode                                   | l <sub>VSdom</sub>          | 200  | 700  | 950  | μA   | Bus dominant (internal<br>LIN pull-up resistor<br>active)<br>V <sub>VS</sub> < 14V<br>without load at VCC |

| 1.6 | Supply Current in Fail-Safe Mode                                   | I <sub>VSfail</sub>         | 40   | 55   | 80   | μA   | Bus recessive<br>5.5V < V <sub>VS</sub> < 14V<br>without load at VCC                                      |

|     |                                                                    | I <sub>VSfail</sub>         | 50   | 130  | 170  | μA   | Bus recessive<br>2.0V < V <sub>VS</sub> < 5.5V<br>without load at VCC                                     |

| 1.7 | VS Undervoltage<br>Threshold                                       | $V_{VS\_th\_U\_down}$       | 3.9  | 4.3  | 4.7  | V    | Decreasing supply voltage                                                                                 |

|     | (Switching from<br>Normal to Fail-<br>Safe Mode)                   | V <sub>VS_th_U_up</sub>     | 4.1  | 4.6  | 4.9  | V    | Increasing supply voltage                                                                                 |

| 1.8 | VS Undervoltage<br>Hysteresis                                      | V <sub>VS_hys_F_N</sub>     | 0.1  | 0.25 | 0.4  | V    |                                                                                                           |

## **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics**: Unless otherwise indicated, all values are specified for  $5V < V_{VS} < 28V$ ,  $-40^{\circ}C < T_{VJ} < +150^{\circ}C$  and refer to the GND pin.

|      | < T <sub>vJ</sub> < +150°C and r  Parameters                  |                       | Min.                    | Ti <sub>sm</sub>        | Max.                    | Unit | Conditions                                                                |

|------|---------------------------------------------------------------|-----------------------|-------------------------|-------------------------|-------------------------|------|---------------------------------------------------------------------------|

| No.  |                                                               | Symbol                |                         | Тур.                    |                         |      |                                                                           |

| 1.9  | VS Operation<br>Threshold                                     | $V_{VS\_th\_U\_down}$ | 1.9                     | 2.05                    | 2.3                     | V    | Switch to unpowered mode                                                  |

|      | (Switching to<br>Unpowered Mode)                              | $V_{VS\_th\_U\_up}$   | 2.0                     | 2.25                    | 2.4                     | V    | Switch from<br>unpowered to Fail-<br>Safe mode                            |

| 1.10 | VS Undervoltage<br>Hysteresis                                 | $V_{VS\_hys\_U}$      | 0.1                     | 0.2                     | 0.3                     | V    |                                                                           |

| 2    | RXD Output Pin (o                                             | nly SBC)              |                         |                         |                         |      |                                                                           |

| 2.1  | Low-Level Output<br>Sink Capability                           | V <sub>RXDL</sub>     | _                       | 0.2                     | 0.4                     | V    | Normal mode,<br>V <sub>LIN</sub> = 0V,<br>I <sub>RXD</sub> = 2 mA         |

| 2.2  | High-Level Output<br>Source Capability                        | $V_{RXDH}$            | V <sub>VCC</sub> - 0.4V | V <sub>VCC</sub> - 0.2V | _                       | V    | Normal mode $V_{LIN} = V_{VS}$ , $I_{RXD} = -2 \text{ mA}$                |

| 3    | TXD Input/Output I                                            | Pin (only SBC)        |                         |                         |                         |      |                                                                           |

| 3.1  | Low-Level Voltage Input                                       | $V_{TXDL}$            | -0.3                    | _                       | +0.8                    | V    |                                                                           |

| 3.2  | High-Level<br>Voltage Input                                   | $V_{TXDH}$            | 2                       | _                       | V <sub>VCC</sub> + 0.3V | V    |                                                                           |

| 3.3  | Pull-Up Resistor                                              | $R_{TXD}$             | 40                      | 70                      | 100                     | kΩ   | V <sub>TXD</sub> = 0V                                                     |

| 3.4  | High-Level<br>Leakage Current                                 | I <sub>TXD</sub>      | -3                      | _                       | +3                      | μA   | $V_{TXD} = V_{VCC}$                                                       |

| 3.7  | Low-Level Output<br>Sink Current at<br>LIN Wake-Up<br>Request | I <sub>TXD</sub>      | 2                       | 2.5                     | 8                       | mA   | Fail-Safe mode V <sub>LIN</sub> = V <sub>VS</sub> V <sub>TXD</sub> = 0.4V |

| 1    | <b>EN Input Pin (only</b>                                     | SBC)                  |                         |                         |                         |      |                                                                           |

| 1.1  | Low-Level Voltage<br>Input                                    | V <sub>ENL</sub>      | -0.3                    | _                       | +0.8                    | V    |                                                                           |

| 1.2  | High-Level<br>Voltage Input                                   | V <sub>ENH</sub>      | 2                       | _                       | V <sub>VCC</sub> + 0.3V | V    |                                                                           |

| 1.3  | Pull-Down<br>Resistor                                         | R <sub>EN</sub>       | 50                      | 125                     | 200                     | kΩ   | V <sub>EN</sub> = V <sub>VCC</sub>                                        |

| 1.4  | Low-Level Input<br>Current                                    | I <sub>EN</sub>       | -3                      | _                       | +3                      | μA   | V <sub>EN</sub> = 0V                                                      |

| 5    | NRES Open Drain                                               | Output Pin            |                         |                         |                         |      |                                                                           |

| 5.1  | Low-Level Output<br>Voltage                                   | $V_{NRESL}$           |                         | 0.2                     | 0.4                     | V    | $V_{VS} \ge 5.5V$<br>$I_{NRES} = 2 \text{ mA}$                            |

| 5.2  | Undervoltage<br>Reset Time                                    | t <sub>Reset</sub>    | 2                       | 4                       | 6                       | ms   | $V_{VS} \ge 5.5V$ $C_{NRES} = 20 \text{ pF}$                              |

| 5.3  | Reset Debounce<br>Time for Falling<br>Edge                    | t <sub>res_f</sub>    | 0.5                     | _                       | 10                      | μs   | V <sub>VS</sub> ≥ 5.5V<br>C <sub>NRES</sub> = 20 pF                       |

| 5.4  | Switch Off<br>Leakage Current                                 | I <sub>NRES_L</sub>   | -3                      | _                       | +3                      | μA   | V <sub>NRES</sub> = 5.5V                                                  |

## **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics**: Unless otherwise indicated, all values are specified for  $5V < V_{VS} < 28V$ ,  $-40^{\circ}C < T_{VJ} < +150^{\circ}C$  and refer to the GND pin.

|      | < I <sub>vJ</sub> < +150°C and                                     | · ·                         |                                  |      | 1     | 1    |                                                                      |

|------|--------------------------------------------------------------------|-----------------------------|----------------------------------|------|-------|------|----------------------------------------------------------------------|

| No.  | Parameters                                                         | Symbol                      | Min.                             | Тур. | Max.  | Unit | Conditions                                                           |

| 8    | VCC Voltage Regu                                                   | lator (3.3V)                |                                  |      |       |      |                                                                      |

| 8.1  | Output Voltage<br>V <sub>VCC</sub>                                 | V <sub>VCCnor</sub>         | 3.234                            | _    | 3.366 | V    | 4V < V <sub>VS</sub> < 18V<br>(0 mA to 50 mA)                        |

|      |                                                                    | $V_{VCCnor}$                | 3.234                            | _    | 3.366 | V    | 4.5V < V <sub>VS</sub> < 18V<br>(0 mA to 85 mA)<br>( <b>Note 2</b> ) |

| 8.2  | Output Voltage<br>V <sub>VCC</sub> at Low V <sub>VS</sub>          | V <sub>VCClow</sub>         | $V_{VS} - V_{D}$                 | _    | 3.366 | V    | 3V < V <sub>VS</sub> < 4V                                            |

| 8.3  | Regulator Drop<br>Voltage                                          | V <sub>D1</sub>             | _                                | 100  | 150   | mV   | $V_{VS} > 3V$ ,<br>$I_{VCC} = -15 \text{ mA}$                        |

| 8.4  | Regulator Drop<br>Voltage                                          | $V_{D2}$                    | _                                | 300  | 500   | mV   | $V_{VS} > 3V$ ,<br>$I_{VCC} = -50 \text{ mA}$                        |

| 8.5  | Line Regulation<br>Maximum                                         | VCC <sub>line</sub>         | _                                | 0.1  | 0.2   | %    | 4V < V <sub>VS</sub> < 18V                                           |

| 8.6  | Load Regulation<br>Maximum                                         | VCC <sub>load</sub>         | _                                | 0.1  | 0.5   | %    | 5 mA < I <sub>VCC</sub> < 50 mA                                      |

| 8.7  | Output Current<br>Limitation                                       | I <sub>VCClim</sub>         | _                                | -180 | -120  | mA   | V <sub>VS</sub> > 4V                                                 |

| 8.8  | Load Capacity                                                      | C <sub>load</sub>           | 1.8                              | 2.2  | _     | μF   | MLC capacitor (Note 3)                                               |

| 8.9  | VCC Undervoltage<br>Threshold<br>(NRES ON)                         | V <sub>VCC_th_uv_down</sub> | 2.3                              | 2.5  | 2.8   | V    | Referred to VCC<br>V <sub>VS</sub> > 4V                              |

|      | Vcc Undervoltage<br>Threshold<br>(NRES OFF)                        | V <sub>VCC_th_uv_up</sub>   | 2.5                              | 2.6  | 2.9   | V    | Referred to VCC<br>V <sub>VS</sub> > 4V                              |

| 8.10 | Hysteresis of VCC<br>Undervoltage<br>Threshold                     | V <sub>VCC_hys_uv</sub>     | 100                              | 200  | 300   | mV   | Referred to VCC<br>V <sub>VS</sub> > 4V                              |

| 8.11 | Ramp-Up Time<br>V <sub>VS</sub> > 4V to<br>V <sub>VCC</sub> = 3.3V | tvcc                        | 1                                | 1.5  | ms    | А    | $C_{VCC}$ = 2.2 µF<br>$I_{load}$ = -5 mA at VCC                      |

| 9    | VCC Voltage Regu                                                   | lator (5V)                  |                                  |      |       | •    |                                                                      |

| 9.1  | Output Voltage<br>V <sub>VCC</sub>                                 | V <sub>VCCnor</sub>         | 4.9                              | _    | 5.1   | V    | 5.5V < V <sub>VS</sub> < 18V<br>(0 mA to 50 mA)                      |

|      |                                                                    | V <sub>VCCnor</sub>         | 4.9                              | _    | 5.1   | V    | 6V < V <sub>VS</sub> < 18V<br>(0 mA to 85 mA)<br>( <b>Note 2</b> )   |

| 9.2  | Output Voltage<br>V <sub>VCC</sub> at Low V <sub>VS</sub>          | V <sub>VCClow</sub>         | V <sub>VS</sub> - V <sub>D</sub> | _    | 5.1   | V    | 4V < V <sub>VS</sub> < 5.5V                                          |

| 9.3  | Regulator Drop<br>Voltage                                          | V <sub>D1</sub>             | _                                | 100  | 200   | mV   | $V_{VS} > 4V$ ,<br>$I_{VCC} = -20 \text{ mA}$                        |

| 9.4  | Regulator Drop<br>Voltage                                          | V <sub>D1</sub>             | _                                | 300  | 500   | mV   | $V_{VS} > 4V$ ,<br>$I_{VCC} = -50 \text{ mA}$                        |

| 9.5  | Regulator Drop<br>Voltage                                          | V <sub>D3</sub>             | _                                | _    | 150   | mV   | $V_{VS} > 3.3V$ ,<br>$I_{VCC} = -15 \text{ mA}$                      |

| 9.6  | Line Regulation<br>Maximum                                         | VCC <sub>line</sub>         | _                                | 0.1  | 0.2   | %    | 5.5V < V <sub>VS</sub> < 18V                                         |

### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

Electrical Characteristics: Unless otherwise indicated, all values are specified for 5V < V<sub>VS</sub> < 28V, -40°C < T<sub>vJ</sub> < +150°C and refer to the GND pin. No. **Parameters Symbol** Min. Тур. Max. Unit Conditions 9.7 Load Regulation VCC<sub>load</sub> 0.1 0.5  $5 \text{ mA} < I_{VCC} < 50 \text{ mA}$ Maximum Output Current  $V_{VS} > 5.5V$ 9.8 -180 -120 I<sub>VCClim</sub> mΑ Limitation MLC capacitor 9.9 Load Capacity 1.8 2.2  $C_{load}$ (Note 3) VCC Undervoltage Referred to VCC 9.10 4.2 4.4 4.6  $V_{VCC\_th\_uv\_down}$ Threshold  $V_{VS} > 4V$ (NRES ON) VCC Undervoltage 4.3 4.6 4.8 Referred to VCC  $V_{VCC\_th\_uv\_up}$ Threshold  $V_{VS} > 4V$ (NRES OFF) Hysteresis of 100 300 mV Referred to VCC 9.11 200 V<sub>VCC\_hys\_uv</sub> Undervoltage  $V_{VS} > 5.5V$ Threshold Ramp-Up Time 9.12 1 1.5 ms  $C_{VCC}$  = 2.2  $\mu F$  $t_{VCC}$  $V_{VS} > 5.5V \text{ to}$ I<sub>load</sub> = -5 mA at VCC  $V_{VCC} = 5V$ 10 LIN Bus Driver (only SBC): Bus Load Conditions: Load 1 (small): 1 nF, 1 kΩ; Load 2 (large): 10 nF, 500Ω;  $C_{RXD}$  = 20 pF, Load 3 (medium): 6.8 nF, 660Ω characterized on samples 12.7 and 12.8 specifies the timing parameters for proper operation at 20 kb/s and 12.9 and 12.10 at 10.4 kb/s 10.1 **Driver Recessive** 0.9 x V<sub>VS</sub>  $V_{VS}$ Load1/Load2 V<sub>BUSrec</sub> Output Voltage 10.2 **Driver Dominant** 1.2  $V_{VS} = 7V$ V LoSUP Voltage  $R_{load} = 500\Omega$ **Driver Dominant**  $V_{VS} = 18V$ 10.3 2 V <sub>HISUP</sub> Voltage  $R_{load} = 500\Omega$ 10.4 **Driver Dominant** V LoSUP\_1k 0.6  $V_{VS} = 7V$ Voltage  $R_{load}$  = 1000 $\Omega$ 10.5 **Driver Dominant** 8.0  $V_{VS} = 18V$  $V_{HISUP\_1K}$ Voltage  $R_{load} = 1000\Omega$ Pull-Up Resistor to The serial diode is 10.6  $R_{LIN}$ 20 30 47 mandatory 10.7 Voltage Drop at 0.4 1.0 ٧ In pull-up path with V<sub>SerDiode</sub> the Serial Diodes R<sub>slave</sub> I<sub>SerDiode</sub> = 10 mA (Note 3) 10.8 LIN Current 120 200 40 mΑ  $I_{BUS\_LIM}$ Limitation VBUS = VBAT MAX 10.9 Input Leakage -1 Input leakage current -0.35 mΑ IBUS PAS dom Current at the driver off Receiver Includ- $V_{BUS} = 0V$ ing Pull-Up Resis- $V_{BAT} = 12V$ tor as Specified

## **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics**: Unless otherwise indicated, all values are specified for  $5V < V_{VS} < 28V$ ,  $-40^{\circ}C < T_{v,l} < +150^{\circ}C$  and refer to the GND pin.

| No.   | Parameters                                                                                                                                                     | Symbol                   | Min.                    | Тур.                  | Max.                    | Unit | Conditions                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------|-----------------------|-------------------------|------|-----------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                |                          | IVIIII.                 |                       |                         |      |                                                                                               |

| 10.10 | Leakage Current<br>LIN Recessive                                                                                                                               | IBUS_PAS_rec             | _                       | 10                    | 20                      | μA   | Driver off<br>$8V < V_{BAT} < 18V$<br>$8V < V_{BUS} < 18V$<br>$V_{BUS} \ge V_{BAT}$           |

| 10.11 | Leakage Current when the control unit is disconnected from ground. Loss of local ground must not affect communication in the residual network.                 | I <sub>BUS_NO_gnd</sub>  | -10                     | +0.5                  | +10                     | μА   | $GND_{Device} = V_{VS}$<br>$V_{Bat} = 12V$<br>$0V < V_{BUS} < 18V$                            |

| 10.12 | Leakage current at disconnected battery. Node has to sustain the current that can flow under this condition. Bus must remain operational under this condition. | I <sub>BUS_NO_</sub> bat | _                       | 0.1                   | 2                       | μΑ   | V <sub>Bat</sub> disconnected<br>V <sub>SUP_Device</sub> = GND<br>0V < V <sub>BUS</sub> < 18V |

| 10.13 | Capacitance on<br>Pin LIN to GND                                                                                                                               | C <sub>LIN</sub>         | _                       | _                     | 20                      | pF   | Note 3                                                                                        |

| 11    | LIN Bus Receiver (                                                                                                                                             | only SBC)                | <u> </u>                |                       | l.                      |      |                                                                                               |

| 11.1  | Center of Receiver<br>Threshold                                                                                                                                | V <sub>BUS_CNT</sub>     | 0.475 x V <sub>VS</sub> | 0.5 x V <sub>VS</sub> | 0.525 x V <sub>VS</sub> | V    | V <sub>BUS_CNT</sub> = (V <sub>th_dom</sub> + V <sub>th_rec</sub> )/2                         |

| 11.2  | Receiver<br>Dominant State                                                                                                                                     | $V_{BUSdom}$             | -27                     | _                     | 0.4 x V <sub>VS</sub>   | V    | V <sub>EN</sub> = 5V/3.3V                                                                     |

| 11.3  | Receiver<br>Recessive State                                                                                                                                    | $V_{BUSrec}$             | 0.6 x V <sub>VS</sub>   | _                     | 40                      | V    | V <sub>EN</sub> = 5V/3.3V                                                                     |

| 11.4  | Receiver Input<br>Hysteresis                                                                                                                                   | $V_{BUShys}$             | 0.028 x V <sub>VS</sub> | 0.1 x V <sub>VS</sub> | 0.175 x V <sub>VS</sub> | V    | V <sub>hys</sub> =<br>V <sub>th_rec</sub> - V <sub>th_dom</sub>                               |

| 11.5  | Pre-Wake<br>Detection LIN<br>High-Level Input<br>Voltage                                                                                                       | $V_{LINH}$               | V <sub>VS</sub> - 2V    | _                     | V <sub>VS</sub> + 0.3V  | V    |                                                                                               |

| 11.6  | Pre-Wake Detection LIN Low-Level Input Voltage                                                                                                                 | $V_{LINL}$               | -27                     | _                     | V <sub>VS</sub> - 3.3V  | V    | Activates the LIN receiver                                                                    |

| 12    | Internal Timers (or                                                                                                                                            | nly SBC)                 |                         |                       |                         |      |                                                                                               |

| 12.1  | Dominant Time for<br>Wake-Up via LIN<br>Bus                                                                                                                    | t <sub>bus</sub>         | 50                      | 100                   | 150                     | μs   | V <sub>LIN</sub> = 0V                                                                         |

## **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics**: Unless otherwise indicated, all values are specified for  $5V < V_{VS} < 28V$ ,  $-40^{\circ}C < T_{vJ} < +150^{\circ}C$  and refer to the GND pin.

| No.   | Parameters                                                                          | Symbol                                             | Min.  | Тур. | Max.  | Unit | Conditions                                                                                                                                                                                                                                                |

|-------|-------------------------------------------------------------------------------------|----------------------------------------------------|-------|------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.2  | Time Delay for<br>Mode Change<br>from Fail-Safe into<br>Normal Mode via<br>EN Pin   | t <sub>norm</sub>                                  | 5     | 15   | 20    | μs   | V <sub>EN</sub> = 5V/3.3V                                                                                                                                                                                                                                 |

| 12.3  | Time Delay for<br>Mode Change<br>from Normal Mode<br>to Sleep Mode via<br>EN Pin    | <sup>t</sup> sleep                                 | 5     | 15   | 20    | μs   | V <sub>EN</sub> = 0V                                                                                                                                                                                                                                      |

| 12.5  | TXD Dominant<br>Time-Out Time                                                       | t <sub>dom</sub>                                   | 20    | 40   | 60    | ms   | V <sub>TXD</sub> = 0V                                                                                                                                                                                                                                     |

| 12.6  | Time Delay for<br>Mode Change<br>from Silent Mode<br>into Normal Mode<br>via EN Pin | t <sub>s_n</sub>                                   | 5     | 15   | 40    | μs   | V <sub>EN</sub> = 5V/3.3V                                                                                                                                                                                                                                 |

| 12.7  | Duty Cycle 1                                                                        | D1                                                 | 0.396 | _    | _     | _    | $TH_{Rec(max)} = \\ 0.744 \text{ x V}_{VS} \\ TH_{Dom(max)} = \\ 0.581 \text{ x V}_{VS} \\ V_{VS} = 7.0V \text{ to } 18V \\ t_{Bit} = 50 \mu\text{s} \\ D1 = t_{bus\_rec(min)}\text{/} \\ (2 \text{ x } t_{Bit})$                                         |

| 12.8  | Duty Cycle 2                                                                        | D2                                                 | _     | _    | 0.581 | _    | $TH_{Rec(min)} = \\ 0.422 \text{ x V}_{VS} \\ TH_{Dom(min)} = \\ 0.284 \text{ x V}_{VS} \\ V_{VS} = 7.6 \text{V to } 18 \text{V} \\ t_{Bit} = 50  \mu \text{s} \\ D2 = t_{bus\_rec(max)} / \\ (2 \text{ x } t_{Bit})$                                     |

| 12.9  | Duty Cycle 3                                                                        | D3                                                 | 0.417 | _    | _     | _    | $\begin{array}{l} TH_{Rec(max)} = \\ 0.778 \text{ x V}_{VS} \\ TH_{Dom(max)} = \\ 0.616 \text{ x V}_{VS} \\ V_{VS} = 7.0 \text{V to } 18 \text{V} \\ t_{Bit} = 96  \mu \text{s} \\ D3 = t_{bus\_rec(min)} \text{/} \\ (2 \text{ x } t_{Bit}) \end{array}$ |

| 12.10 | Duty Cycle 4                                                                        | D4                                                 | _     | _    | 0.590 | _    | $\begin{array}{l} TH_{Rec(min)} = \\ 0.389 \text{ x V}_{VS} \\ TH_{Dom(min)} = \\ 0.251 \text{ x V}_{VS} \\ V_{VS} = 7.6 \text{V to } 18 \text{V} \\ t_{Bit} = 96  \mu \text{s} \\ D4 = t_{bus\_rec(max)} / \\ (2 \text{ x } t_{Bit}) \end{array}$        |

| 12.11 | Slope Time Fall-<br>ing and Rising<br>Edge at LIN                                   | t <sub>SLOPE_fall</sub><br>t <sub>SLOPE_rise</sub> | 3.5   |      | 22.5  | μs   | V <sub>VS</sub> = 7.0V to 18V                                                                                                                                                                                                                             |

### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

Electrical Characteristics: Unless otherwise indicated, all values are specified for 5V < V<sub>VS</sub> < 28V, -40°C < T<sub>vJ</sub> < +150°C and refer to the GND pin. Unit No. **Parameters Symbol** Min. Тур. Max. **Conditions** 13 Receiver Electrical AC Parameters of the LIN Physical Layer (only SBC) LIN Receiver, RXD Load Conditions: C<sub>RXD</sub> = 20 pF Propagation Delay  $V_{VS} = 7.0V \text{ to } 18V$ 13.1 6  $t_{rx\_pd}$ of Receiver  $t_{rx pd} = max(t_{rx pdr},$

t<sub>rx\_sym</sub> Receiver  $t_{rx\_sym} =$ Propagation Delay  $t_{rx\_pdr}$  -  $t_{rx\_pdf}$ Rising Edge Minus Falling Edge 100% correlation tested Note 1:

-2

Characterized on samples

Symmetry of

13.2

Design parameter

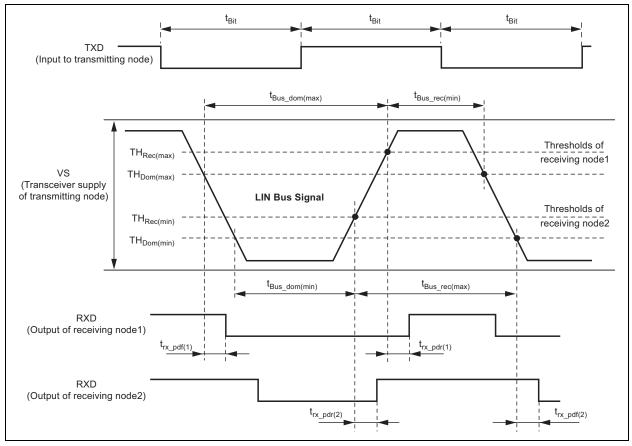

#### FIGURE 2-1: **DEFINITION OF BUS TIMING CHARACTERISTICS**

t<sub>rx\_pdf</sub>)

+2

$V_{VS} = 7.0V \text{ to } 18V$

### **TEMPERATURE SPECIFICATIONS 8-LEAD VDFN**

| Parameters                                                                                                      | Sym.                | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------------------------------|---------------------|------|------|------|------|

| Thermal Resistance Virtual Junction to Exposed Thermal Pad                                                      | R <sub>thvJC</sub>  | _    | 10   | _    | K/W  |

| Thermal Resistance Virtual Junction to Ambient, where Exposed Thermal Pad is Soldered to PCB according to JEDEC | R <sub>thvJA</sub>  | _    | 50   | _    | K/W  |

| Thermal Shutdown of VCC Regulator                                                                               | T <sub>VCCoff</sub> | +150 | +165 | +180 | °C   |

| Thermal Shutdown of LIN Output                                                                                  | T <sub>LINoff</sub> | +150 | +165 | +180 | °C   |

| Thermal Shutdown Hysteresis                                                                                     | T <sub>hys</sub>    | _    | +10  | _    | °C   |

### **TEMPERATURE SPECIFICATIONS 8-LEAD SOIC**

| Parameters                                                                                                        | Sym.                | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------------------------------------------------------------------|---------------------|------|------|------|------|

| Thermal Resistance Virtual Junction to Ambient with a Heat Sink at GND (pin 5) on PCB (fused lead frame to pin 5) | R <sub>thvJA</sub>  |      | 80   | _    | K/W  |

| Thermal Shutdown of VCC Regulator                                                                                 | T <sub>VCCoff</sub> | +150 | +165 | +180 | °C   |

| Thermal Shutdown of LIN Output                                                                                    | T <sub>LINoff</sub> | +150 | +165 | +180 | °C   |

| Thermal Shutdown Hysteresis                                                                                       | T <sub>hys</sub>    |      | +10  | _    | °C   |

#### 3.0 PACKAGING INFORMATION

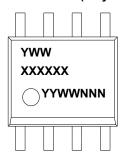

### 3.1 Package Marking Information

8-Lead SOIC (only ATA663254)

Example ATA663254

8-Lead 3 x 3 mm VDFN

Example ATA663201

Example ATA663203

Example ATA663231

Example ATA663254

| Legend: | XXX        | Customer-specific information                              |

|---------|------------|------------------------------------------------------------|

|         | Υ          | Year code (last digit of calendar year)                    |

|         | YY         | Year code (last 2 digits of calendar year)                 |

|         | WW         | Week code (week of January 1 is week '01')                 |

|         | NNN        | Alphanumeric traceability code                             |

|         | <b>e</b> 3 | Pb-free JEDEC designator for Matte Tin (Sn)                |

|         | *          | This package is Pb-free. The Pb-free JEDEC designator (e3) |

|         |            | can be found on the outer packaging for this package.      |

In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

Note:

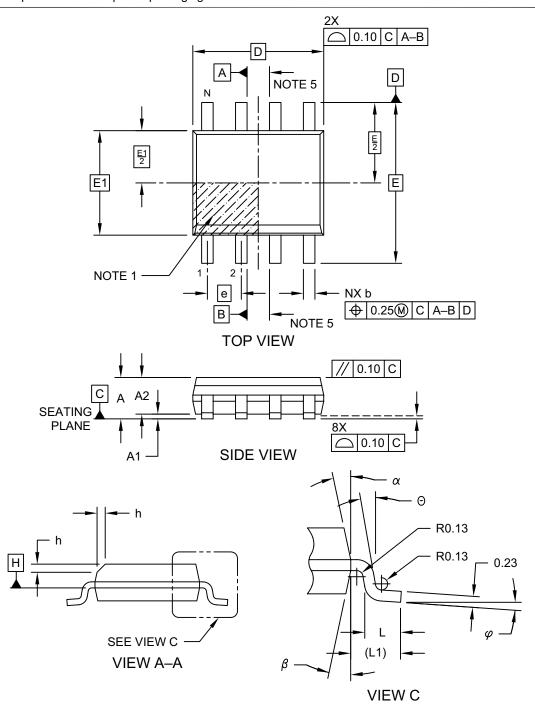

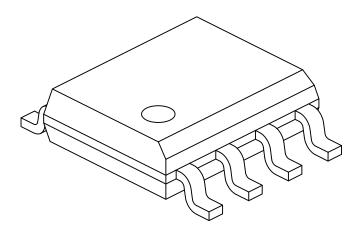

### 8-Lead Plastic Small Outline (OA) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-057-OA Rev D Sheet 1 of 2

### 8-Lead Plastic Small Outline (OA) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |             |          |      |  |  |  |

|--------------------------|-------------|-------------|----------|------|--|--|--|

| Dimension                | MIN         | NOM         | MAX      |      |  |  |  |

| Number of Pins           | N           |             | 8        |      |  |  |  |

| Pitch                    | е           |             | 1.27 BSC |      |  |  |  |

| Overall Height           | Α           | ı           | ı        | 1.75 |  |  |  |

| Molded Package Thickness | A2          | 1.25        |          |      |  |  |  |

| Standoff §               | A1          | 0.10 - 0.2  |          |      |  |  |  |

| Overall Width            | E           | 6.00 BSC    |          |      |  |  |  |

| Molded Package Width     | E1          | 3.90 BSC    |          |      |  |  |  |

| Overall Length           | D           | 4.90 BSC    |          |      |  |  |  |

| Chamfer (Optional)       | h           | 0.25 - 0.50 |          |      |  |  |  |

| Foot Length              | L           | 0.40        | 0.40 - 1 |      |  |  |  |

| Footprint                | L1          | 1.04 REF    |          |      |  |  |  |

| Foot Angle               | φ           | 0°          | 0° -     |      |  |  |  |

| Lead Thickness           | С           | 0.17        | 0.17 -   |      |  |  |  |

| Lead Width               | b           | 0.31        | 0.31 -   |      |  |  |  |

| Mold Draft Angle Top     | α           | 5°          | -        | 15°  |  |  |  |

| Mold Draft Angle Bottom  | β           | 5°          | -        | 15°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-057-OA Rev D Sheet 2 of 2

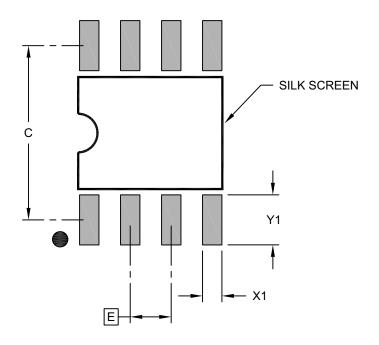

### 8-Lead Plastic Small Outline (OA) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                         | MILLIMETERS |          |         |      |  |

|-------------------------|-------------|----------|---------|------|--|

| Dimension               | Limits      | MIN      | MIN NOM |      |  |

| Contact Pitch           | Е           | 1.27 BSC |         |      |  |

| Contact Pad Spacing     | С           | 5.40     |         |      |  |

| Contact Pad Width (X8)  | X1          | 0.60     |         |      |  |

| Contact Pad Length (X8) | Y1          |          |         | 1.55 |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2057-OA Rev B

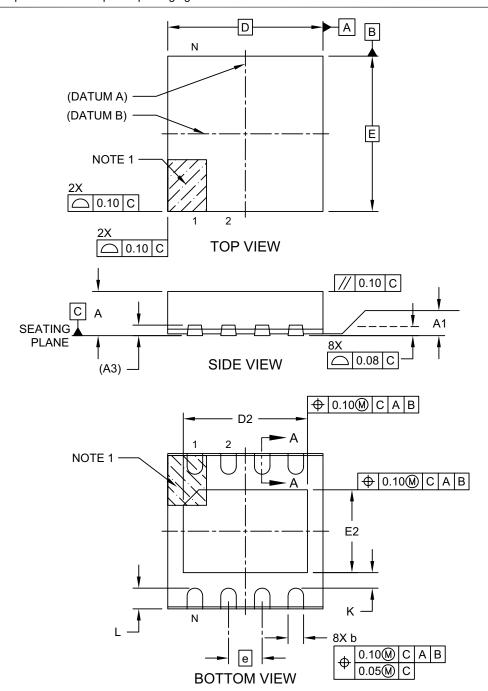

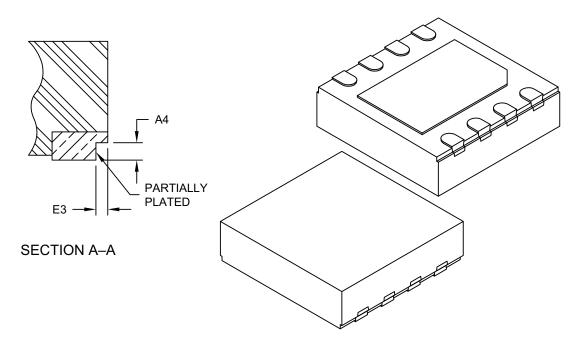

## 8-Lead Very Thin Plastic Dual Flat, No Lead Package (Q8B) - 3x3 mm Body [VDFN] With 2.40x1.60 mm Exposed Pad and Stepped Wettable Flanks; Atmel Legacy YCL

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-21358 Rev C Sheet 1 of 2

## 8-Lead Very Thin Plastic Dual Flat, No Lead Package (Q8B) - 3x3 mm Body [VDFN] With 2.40x1.60 mm Exposed Pad and Stepped Wettable Flanks; Atmel Legacy YCL

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                               | MILLIMETERS                |                |            |      |  |  |

|-------------------------------|----------------------------|----------------|------------|------|--|--|

| Dimension                     | MIN                        | NOM            | MAX        |      |  |  |

| Number of Terminals           | N                          |                | 8          |      |  |  |

| Pitch                         | е                          |                | 0.65 BSC   |      |  |  |

| Overall Height                | Α                          | 0.80           | 0.90       | 1.00 |  |  |

| Standoff                      | A1                         | 0.00           | 0.00 0.035 |      |  |  |

| Terminal Thickness            | A3                         | 0.203 REF      |            |      |  |  |

| Overall Length                | D                          | 3.00 BSC       |            |      |  |  |

| Exposed Pad Length            | Exposed Pad Length D2 2.30 |                |            | 2.50 |  |  |

| Overall Width                 | Е                          | 3.00 BSC       |            |      |  |  |

| Exposed Pad Width             | E2                         | 1.50 1.60 1.70 |            |      |  |  |

| Terminal Width                | b                          | 0.25 0.30 0.35 |            |      |  |  |

| Terminal Length               | L                          | 0.35 0.40 0.45 |            |      |  |  |

| Terminal-to-Exposed-Pad       | K                          | 0.20           | -          | -    |  |  |

| Wettable Flank Step Cut Depth | A4                         | 0.10 - 0.19    |            |      |  |  |

| Wettable Flank Step Cut Width | -                          | -              | 0.085      |      |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M  $\,$

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-21358 Rev C Sheet 2 of 2

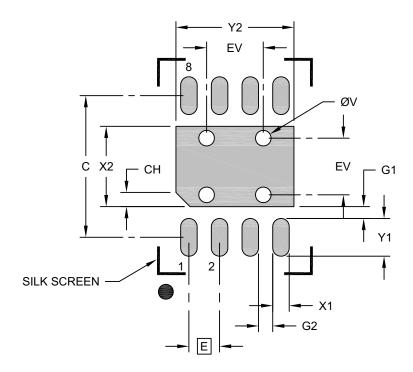

## 8-Lead Very Thin Plastic Dual Flat, No Lead Package (Q8B) - 3x3 mm Body [VDFN] With 2.40x1.60 mm Exposed Pad and Stepped Wettable Flanks

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS     |      |      |      |  |

|---------------------------------|-----------------|------|------|------|--|

| Dimension                       | MIN             | NOM  | MAX  |      |  |

| Contact Pitch                   | Contact Pitch E |      |      |      |  |

| Optional Center Pad Width       | X2              | 1.7  |      |      |  |

| Optional Center Pad Length      | Y2              |      | 2.50 |      |  |

| Contact Pad Spacing             | С               |      | 3.00 |      |  |

| Contact Pad Width (X8)          | X1              |      |      | 0.35 |  |

| Contact Pad Length (X8)         |                 |      | 0.80 |      |  |

| Contact Pad to Center Pad (X8)  | G1              | 0.20 |      |      |  |

| Contact Pad to Contact Pad (X6) | G2              | 0.20 |      |      |  |

| Pin 1 Index Chamfer             | CH              | 0.20 |      |      |  |

| Thermal Via Diameter            | V               |      | 0.33 |      |  |

| Thermal Via Pitch               |                 | 1.20 |      |      |  |

#### Notes:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-23358 Rev C

### APPENDIX A: REVISION HISTORY

### **Revision C (January 2021)**

The following is the list of modifications:

- 1. Updated the VDFN package drawing.

- 2. Updated the Product Identification System section.

- 3. Minor text updates.

### **Revision B (January 2019)**

The following is the list of modifications:

- Updated Parameter 1.4 on page 16.

- Updated the dynamic maximum rating of the VS pin on page 15.

### **Revision A (October 2018)**

- · Original release of this document.

- · Minor text updates.

- This document replaces Atmel -9337G-AUTO-09/16.

NOTES:

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| DART NO                                  | VV                           | ry(1)                                   |                                                                                                            | VVV                                | Exa  | mples | :                                                         |                                                  |                                                                                                                                                                                               |

|------------------------------------------|------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------|------|-------|-----------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PART NO.<br>Device                       | - <u>XX</u><br> <br>Package  | [X] <sup>(1)</sup> Tape and Reel Option | X<br>                                                                                                      | - <u>XXX</u><br> <br>Qualification | a) A | TA663 | 201-GBQW                                                  |                                                  | ATA663201, 8-Lead VDFN,<br>Tape and Reel,<br>RoHS compliant package,<br>Automotive Qualified                                                                                                  |

| Device:                                  | ATA663<br>ATA663             | 3203: 5V Vol                            | oltage Regulator<br>tage Regulator<br>stem Basis Chip,                                                     |                                    | b) A | TA663 | 203-GBQW                                                  |                                                  | ATA663203, 8-Lead VDFN,<br>Tape and Reel,<br>RoHS compliant package,<br>Automotive Qualified                                                                                                  |

|                                          | ATA663                       | Voltag<br>3254: LIN Sy                  | ng LIN Transceiver a<br>e Regulator<br>estem Basis Chip,<br>ng LIN Transceiver a                           |                                    | c) A | TA663 | 231-GBQW                                                  |                                                  | ATA663231, 8-Lead VDFN,<br>Tape and Reel,<br>RoHS compliant package,<br>Automotive Qualified                                                                                                  |

| Package:                                 | GA =                         | Voltag<br>8-Lead SOIC                   | e Regulator                                                                                                |                                    | d) A | TA663 | 254-GAQW                                                  |                                                  | ATA663254, 8-Lead SOIC,<br>Tape and Reel,<br>RoHS compliant package,<br>Automotive Qualified                                                                                                  |

| Tape and Reel<br>Option:                 | GB = Q =                     | 8-Lead VDFN 330 mm diam                 | eter Tape and Reel <sup>(1)</sup>                                                                          |                                    | e) A | TA663 | 254-GBQW                                                  |                                                  | ATA663254, 8-Lead VDFN,<br>Tape and Reel,<br>RoHS compliant package,<br>Automotive Qualified                                                                                                  |

| Package<br>Directives<br>Classification: | W =                          | Package is Ro                           | oHS compliant <sup>(2)</sup>                                                                               |                                    | f) A | TA663 | 254-GAQW                                                  |                                                  | ATA663254, 8-Lead SOIC,<br>Tape and Reel,<br>RoHS compliant package,<br>Automotive Qualified                                                                                                  |

| Qualification:                           | VAO =<br>blank=              | Automotive<br>Automotive                |                                                                                                            |                                    | g) A | TA663 | 254-GBQW                                                  |                                                  | ATA663254, 8-Lead VDFN,<br>Tape and Reel,<br>RoHS compliant package,<br>Automotive Qualified                                                                                                  |

| Du<br>the                                | e to a new no<br>suffix -VAO | omenclature, the a                      | eet are Automotive qua<br>automotive qualified de<br>as regards the qualifica<br>vices listed in this data | evices will get<br>ation, there is | h) A | TA663 | 231-GBQW                                                  |                                                  | ATA663231, 8-Lead VDFN,<br>Tape and Reel,<br>RoHS compliant package,<br>Automotive Qualified                                                                                                  |